Using Assembly Language with C/C+++

Using Assembly Language with C/C++

1. Pengertian Compiler Switch

Compiler switch (atau sering disebut flag) adalah sebuah parameter atau perintah tambahan yang Anda sertakan saat mengkompilasi program. Perintah ini berfungsi untuk mengubah cara kerja kompiler, misalnya untuk mengaktifkan fitur tertentu, menampilkan peringatan (warnings), atau—seperti dalam kasus ini—melakukan optimasi untuk perangkat keras spesifik. Switch di sini ditandai dengan awalan /G.

2. Fungsi Opsi /G

/G1(Target: 8088/8086): Opsi ini menginstruksikan compiler untuk menghasilkan kode yang kompatibel dengan prosesor paling dasar dalam keluarga x86, yaitu Intel 8088 dan 8086. Kode yang dihasilkan menggunakan set instruksi 16-bit standar tanpa adanya fitur-fitur modern. Ini memastikan kompatibilitas maksimal dengan perangkat keras lawas yang menjadi cikal bakal komputer pribadi (PC)./G2(Target: 80188/80186/80286): Opsi ini menargetkan generasi prosesor berikutnya. Intel 80188/80186 menambahkan beberapa instruksi baru yang lebih efisien, dan 80286 memperkenalkan "protected mode" yang menjadi dasar untuk multitasking. Dengan memilih/G2, compiler akan memanfaatkan instruksi tambahan tersebut untuk menghasilkan kode yang sedikit lebih cepat dan efisien dibandingkan target/G1./G3(Target: 80386): Ini adalah lompatan besar karena 80386 merupakan prosesor 32-bit pertama dalam keluarga Intel. Menggunakan switch/G3memungkinkan compiler untuk menghasilkan kode yang memanfaatkan arsitektur 32-bit, termasuk register yang lebih besar dan mode memori yang lebih canggih. Ini membuka jalan untuk aplikasi yang lebih kuat dan sistem operasi modern./G4(Target: 80486): Prosesor 80486 mengintegrasikan math co-processor (untuk operasi matematika floating-point) langsung ke dalam chip dan memperkenalkan on-chip cache L1. Opsi/G4akan mengoptimalkan kode untuk memanfaatkan fitur-fitur ini, terutama untuk aplikasi yang banyak melakukan perhitungan matematika, sehingga menghasilkan performa yang jauh lebih kencang./G5(Target: Pentium): Generasi Pentium memperkenalkan arsitektur superskalar, yang berarti prosesor dapat menjalankan lebih dari satu instruksi dalam satu siklus jam (clock cycle). Compiler yang menargetkan Pentium (/G5) akan mengatur ulang instruksi dalam kode untuk memaksimalkan eksekusi paralel ini, sebuah teknik yang dikenal sebagai instruction pairing./G6(Target: Pentium Pro hingga Pentium 4): Opsi ini mencakup keluarga arsitektur P6. Prosesor seperti Pentium Pro, Pentium II, III, dan 4 memperkenalkan fitur-fitur canggih seperti out-of-order execution dan pipelining yang lebih dalam. Menggunakan/G6, compiler akan menghasilkan kode yang dioptimalkan untuk arsitektur modern ini, yang sangat berbeda dari generasi sebelumnya dan mampu memberikan peningkatan performa yang signifikan.

## Intel 8088 / 8086

Ini adalah fondasi dari arsitektur x86. Spesifikasinya, menurut standar modern, sangat dasar, tetapi revolusioner pada masanya.

Spesifikasi Intel 8086 / 8088 Tahun Rilis 1978 (8086), 1979 (8088) Lebar Data Internal 16-bit Lebar Data Eksternal (Bus) 16-bit (8086), 8-bit (8088) Lebar Alamat (Address Bus) 20-bit Memori Maksimum 2^20 = 1 MB Kecepatan Clock Umumnya 5 MHz hingga 10 MHz Jumlah Transistor ~29.000 Fitur Kunci - Arsitektur 16-bit pertama dari Intel<br>- Mode operasi tunggal (Real Mode)<br>- Menggunakan set instruksi x86 awal

Ini adalah fondasi dari arsitektur x86. Spesifikasinya, menurut standar modern, sangat dasar, tetapi revolusioner pada masanya.

| Spesifikasi | Intel 8086 / 8088 |

| Tahun Rilis | 1978 (8086), 1979 (8088) |

| Lebar Data Internal | 16-bit |

| Lebar Data Eksternal (Bus) | 16-bit (8086), 8-bit (8088) |

| Lebar Alamat (Address Bus) | 20-bit |

| Memori Maksimum | 2^20 = 1 MB |

| Kecepatan Clock | Umumnya 5 MHz hingga 10 MHz |

| Jumlah Transistor | ~29.000 |

| Fitur Kunci | - Arsitektur 16-bit pertama dari Intel<br>- Mode operasi tunggal (Real Mode)<br>- Menggunakan set instruksi x86 awal |

Konfigurasi Mode Minimum 8086 digunakan untuk sistem kecil dengan prosesor tunggal dan Konfigurasi Mode Maksimum 8086 untuk sistem ukuran sedang hingga besar, yang sering kali menyertakan dua prosesor atau lebih. Gambar 10.1 menunjukkan Diagram Pin Mikroprosesor 8086 dan Diagram Pin 8088 dalam mode minimum maupun maksimum. Seperti yang terungkap dari perbandingan dekat, tidak ada banyak perbedaan antara dua mikroprosesor – keduanya dikemas dalam paket dual-in-line (DIPS) 40-pin. Seperti yang disebutkan dalam bab 1, 8086 adalah mikroprosesor 16-bit dengan bus data 16-bit, dan 8088 adalah mikroprosesor 16-bit dengan bus data 8-bit. Pin-out menunjukkan, 8086 memiliki koneksi pin AD 0 -AD 15 , dan 8088 memiliki koneksi pin AD 0 -AD 7 . Ada satu perbedaan kecil lagi dalam salah satu sinyal kontrol. 8086 memiliki pin M/IO, dan 8088 memiliki pin 10/M. Perbedaan perangkat keras hanya terdapat pada pin 34 kedua chip: pada 8086, pinnya adalah BHE/S 7 , sedangkan pada 8088, pinnya adalah SS 0 .

Pin-pin 8086/8088

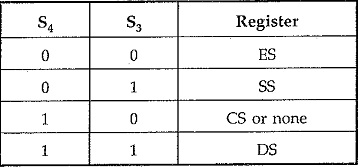

2.A19 /S6 -A16 / S3 : Selama bagian pertama siklus mesin , register ini digunakan untuk mengeluarkan 4 bit alamat teratas. Selama sisa siklus mesin, register ini digunakan untuk mengeluarkan status, yang menunjukkan jenis operasi yang akan dilakukan dalam siklus tersebut. S3 dan S4 menunjukkan register segmen yang digunakan sebagai berikut:

S 5 memberikan pengaturan bendera interupsi (IF) saat ini dan S 6 selalu nol.

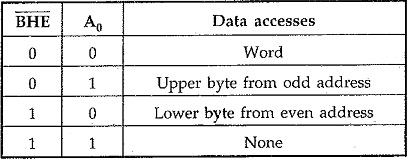

3.BHE/S 7 : BHE (Bus High Enable) : Rendah pada pin ini selama bagian pertama siklus mesin, mengindikasikan bahwa sedikitnya satu byte transfer arus harus dilakukan pada byte orde lebih tinggi AD 15 -AD 8 ; jika tidak, transfer dilakukan pada byte orde lebih rendah AD 7 -AD 0 .

Status S 7 dikeluarkan selama bagian akhir siklus mesin, tetapi, saat ini, S 7 belum diberi makna.

4.NMI : Ini adalah permintaan interupsi nortmaskable yang dipicu tepi positif,

5.INTR: Ini adalah permintaan interupsi yang dapat ditutup dan dipicu oleh level. Permintaan ini diambil sampelnya selama siklus clock terakhir setiap instruksi untuk menentukan apakah prosesor harus memasuki rutinitas layanan interupsi.

6.CLK: 8086 membutuhkan sinyal clock (dengan siklus kerja 33%) dari beberapa generator eksternal yang dikontrol kristal untuk menyinkronkan operasi internal. Frekuensi clock bergantung

7.RESET: Menghapus PSW, IP, DS, SS, ES, dan antrean instruksi. Kemudian, CS diatur ke FITIMI. Sinyal ini harus tinggi setidaknya selama 4 siklus clock. Ketika RESET dihapus, 8086 akan mengambil instruksi berikutnya dari alamat fisik FEFFOH.

8.READY: Jika sinyal ini rendah, 8086 memasuki status tunggu. Sinyal ini terutama digunakan untuk menyinkronkan periferal yang lebih lambat dengan mikroprosesor.

9. TEST (Input): Sinyal ini hanya digunakan oleh instruksi WAIT. 8086 memasukistatus tunggu setelah instruksi WAIT dieksekusi hingga sinyal RENDAH muncul pada pin TEST. Sinyal TEST disinkronkan secara internal selama setiap siklus clock pada tepi terdepan siklus clock.

10.RD (Output) : RD rendah setiap kali 8086 membaca data dari memori atau perangkat I/O.

11. MN/MX (Input): 8086 dapat dikonfigurasi dalam mode minimum atau mode maksimum menggunakan pin ini. Pin ini terhubung ke mode minimum.

12.VCC

Masukan catu daya menyediakan sinyal +5,0 volt toleransi 10 persen ke microprocessor.

13.GND

Hubungan ground jalur kembali catu daya.

14. Pin-pin Mode Minimum

Operasi mode minimum 8086/8088 didapat dengan menghubungkan pin MN/MX langsung ke +5,0 volt. Jangan hubungkan pin ini ke +5,0 volt melalui register pull-up karena tidak akan berfungsi dengan benar.

- IO/M

Pin IO/M (8088) atau pin M/IO (8086) akan memilih memory (M/IO) atau I/O.

- WR

Jalur write merupakan strobe yang menunjukkan bahwa 8086/8088 sedang mengeluarkan data ke memory atau I/O.

- INTA

Sinyal interrupt acknowledge merupakan tanggapan terhadap pin INTR.

- ALE

Merupakan address latch enable menunjukkan bahwa bus alamat atau data 8086/8088 berisi informasi alamat.

- DT/R

Sinyal data transmit atau receive.

- DEN

Data bus enable mengaktifkan buffer bus data external.

- HOLD

Masukan hold akan meminta direct memory access DMA.

- HLDA

Merupakan hold acknowledge yang menunjukkan bahwa 8086/8088 memasuki status hold.

15. Pin Mode Maximum

Untuk mencapai mode maximum untuk penggunaan dengan co-processor external, hubungkan pin MN/MX ke ground.

- S0, S1, dan S0

Bit-bit status ini menunjukkan fungsi siklus bus saat itu. Sinyal-sinyal ini biasanya decode oleh bus controller 8288.

- RO/GT1

Pin-pin request atau grant ini meminta DMA selama operasi mode dan maksimum. Jalur-jalur ini dua arah bidirectional dan digunakan RO/GT1 untuk meminta dan memberi hak operasi DMA.

- LOCK

Keluaran lock digunakan untuk mengunci peripheral dari sistem. Pin ini diaktifkan dengan menggunakan awalan LOCK untuk semua instruksi.

- QS1 dan QS0

Bit status menunjukkan status antrian instruksi internal.

## Intel 80486 (i486)

i486 tidak mengubah arsitektur dasar dari i386, tetapi mengintegrasikan banyak fitur dan mengoptimalkannya untuk kecepatan yang jauh lebih tinggi. Ini adalah tentang kinerja dan efisiensi.

Spesifikasi Intel 80486DX Tahun Rilis 1989 Lebar Data Internal 32-bit Lebar Data Eksternal (Bus) 32-bit Lebar Alamat (Address Bus) 32-bit Memori Maksimum Fisik: 4 GB Kecepatan Clock 25 MHz hingga 100 MHz (pada varian DX4) Jumlah Transistor ~1,2 juta Fitur Kunci - Math Co-processor (FPU) terintegrasi: Perhitungan matematika floating-point super cepat.<br>- 8 KB Level 1 (L1) Cache terintegrasi: Memori internal super cepat untuk data yang sering diakses.<br>- Set instruksi yang dioptimalkan (beberapa instruksi hanya butuh 1 siklus clock).<br>- Mendukung burst mode untuk akses memori lebih cepat.

i486 tidak mengubah arsitektur dasar dari i386, tetapi mengintegrasikan banyak fitur dan mengoptimalkannya untuk kecepatan yang jauh lebih tinggi. Ini adalah tentang kinerja dan efisiensi.

| Spesifikasi | Intel 80486DX |

| Tahun Rilis | 1989 |

| Lebar Data Internal | 32-bit |

| Lebar Data Eksternal (Bus) | 32-bit |

| Lebar Alamat (Address Bus) | 32-bit |

| Memori Maksimum | Fisik: 4 GB |

| Kecepatan Clock | 25 MHz hingga 100 MHz (pada varian DX4) |

| Jumlah Transistor | ~1,2 juta |

| Fitur Kunci | - Math Co-processor (FPU) terintegrasi: Perhitungan matematika floating-point super cepat.<br>- 8 KB Level 1 (L1) Cache terintegrasi: Memori internal super cepat untuk data yang sering diakses.<br>- Set instruksi yang dioptimalkan (beberapa instruksi hanya butuh 1 siklus clock).<br>- Mendukung burst mode untuk akses memori lebih cepat. |

Intel 80486, yang diperkenalkan pada tahun 1989, merupakan evolusi besar dari pendahulunya dengan fokus pada kecepatan dan integrasi. Meskipun tetap menggunakan arsitektur 32-bit, IC ini mengintegrasikan komponen yang sebelumnya terpisah, yaitu Math Co-processor (FPU) dan cache memori internal sebesar 8 KB. Dengan lebih dari 1,2 juta transistor dan kecepatan clock yang mencapai 100 MHz pada versi selanjutnya, 80486 menawarkan peningkatan kinerja yang signifikan, sering kali dua kali lipat dari 80386 pada kecepatan yang sama, menjadikannya standar untuk aplikasi yang lebih berat pada masanya.

Varian Penting:

80486SX: Versi lebih murah dengan FPU yang dinonaktifkan.

80486DX2: Memperkenalkan teknologi "clock-doubling", di mana kecepatan internal prosesor dua kali lebih cepat dari kecepatan bus motherboard (misalnya, CPU 66 MHz di motherboard 33 MHz).

Pin-pin 8086/8088

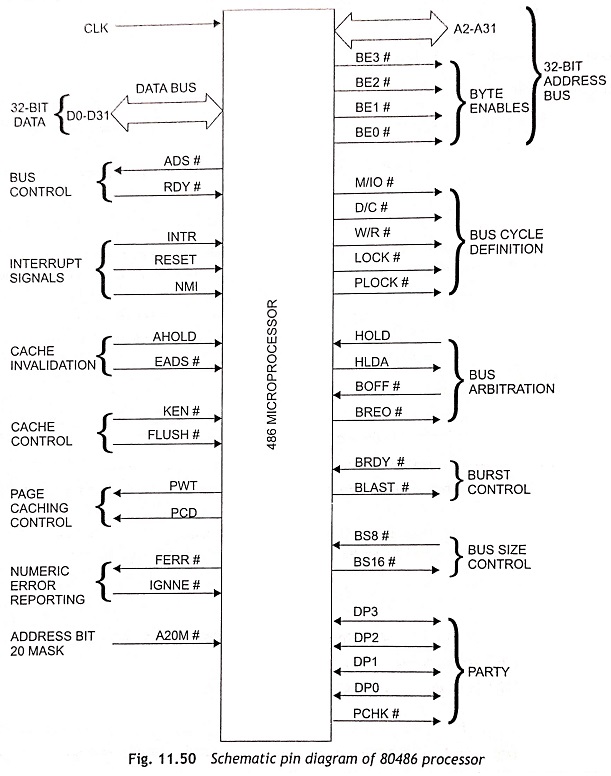

Kelompok Definisi Siklus Bus

M/I̅O̅ Pin keluaran M/I̅O̅ digunakan untuk membedakan antara operasi memori dan I/O.

W/R̅ Pin keluaran W/R̅ digunakan untuk membedakan antara siklus bus baca dan tulis.

D/C̅: Pin keluaran ini dapat digunakan untuk membedakan antara operasi data dan kontrol.

L̅O̅C̅K̅ Pin keluaran ini digunakan untuk menyatakan bahwa siklus bus saat ini terkunci.

P̅L̅O̅C̅K̅ Pin keluaran P̅L̅O̅C̅K̅ (pseudo lock) menunjukkan bahwa operasi saat ini membutuhkan lebih dari satu siklus bus untuk menyelesaikan tugas. Sinyal ini berada pada level logika 0 untuk operasi koprosesor aritmatika.

Grup Kontrol Bus

A̅D̅S̅ Pin keluaran A̅D̅S̅ (address data strobe) menunjukkan bahwa bus alamat berisi alamat memori yang valid.

R̅D̅Y̅ Pin masukan R̅D̅Y̅ (siap) bertindak sebagai sinyal siap dan sinyal ini digunakan untuk siklus non-burst saat ini.

Grup Kontrol Ledakan

B̅R̅D̅Y̅ Pin input B̅R̅D̅Y̅ (siap burst) menunjukkan mode burst pembacaan memori atau operasi memori. Selama mode burst, kecepatan akses memori dapat menjadi dua kali lipat dibandingkan dengan operasi baca/tulis memori normal.

B̅L̅A̅S̅T̅ Ketika sinyal keluaran B̅L̅A̅S̅T̅ (burst last) tinggi, ini menandakan bahwa CPU memulai mode burst akses memori. Jika sinyal ini rendah, ini menandakan bahwa siklus bus burst telah selesai dan sinyal B̅R̅D̅Y̅ selanjutnya diaktifkan untuk memulai operasi akses memori berikutnya.

Kelompok Arbitrase Bus

HOLD Pin HOLD berfungsi sebagai input penahan bus lokal. Pin ini dapat diaktifkan oleh master bus lain seperti pengontrol DMA. Pin ini secara fungsional mirip dengan pin BREQ.

HLDA Sinyal keluaran HLDA digunakan untuk mengakui penerimaan permintaan HOLD yang valid.

BREQ Ketika sinyal keluaran BREQ (permintaan bus) aktif-tinggi, ini menunjukkan bahwa CPU 80486 telah menghasilkan permintaan bus internal.

B̅O̅F̅F̅ Ketika pin masukan B̅O̅F̅F̅ (back off) berada pada level logika 1, CPU 80486 menempatkan bus-busnya pada status hold. Sinyal masukan back off aktif-tinggi memaksa master bus CPU 80486 saat ini untuk melepaskan bus pada siklus clock berikutnya.

Interupsi

INTR Pin INTR adalah input interupsi yang dapat ditutup. Pin ini dikontrol oleh IF dalam register bendera.

NMI Ini adalah masukan interupsi tipe-2 yang tidak dapat ditutup-tutupi.

RESET Pin masukan RESET digunakan untuk mengatur ulang prosesor saat nilainya menjadi tinggi.

Grup Kontrol Cache

K̅E̅N̅ Pin input K̅E̅N̅ (cache enable) digunakan untuk memutuskan apakah siklus saat ini dapat di-cache atau tidak.

F̅L̅U̅S̅H̅ F̅L̅U̅S̅H̅ adalah sinyal masukan untuk membersihkan cache. Ketika pin ini diaktifkan, isi cache dan bit validitas akan dihapus.

Grup Pembatalan Cache

AHOLD Sinyal input AHOLD (permintaan penahanan alamat) memungkinkan master bus lainnya menggunakan bus sistem 80486 untuk siklus pembatalan cache.

E̅A̅D̅S̅ Sinyal masukan E̅A̅D̅S̅ (alamat eksternal) digunakan untuk menunjukkan bahwa alamat yang valid untuk siklus bus eksternal tersedia pada bus alamat.

Kelompok Kemampuan Cache Halaman

PCD Pin keluaran PCD (page cache disable) mencerminkan status bit atribut PCD dalam tabel halaman atau entri direktori halaman.

PWT Pin keluaran PWT (page write-through) menunjukkan status bit atribut PWT dalam tabel halaman atau entri direktori halaman.

Kelompok Kontrol Ukuran Bus

B̅S̅8̅ Pin input B̅S̅8̅ (ukuran bus 8) digunakan untuk fitur ukuran bus dinamis 8-bit 80486 dan 80486 dapat dihubungkan dengan perangkat eksternal 8-bit.

B̅S̅1̅6̅ Pin input B̅S̅1̅6̅ (ukuran bus 16) digunakan untuk fitur ukuran bus dinamis 16-bit dari 80486 dan 80486 dapat dihubungkan dengan perangkat eksternal 16-bit.

A̅2̅0̅M̅ Ketika pin input A̅2̅0̅M̅ (masker bit alamat 20) diaktifkan, 80486 akan menutupi baris alamat fisik A20 sebelum menjalankan siklus memori atau cache. Hal ini sangat berguna untuk membungkus ruang alamat fisik dari 00FFFFH hingga 000000H seperti yang dilakukan mikroprosesor 8086, dan bekerja di sekitar ukuran memori 1 Mbyte. Yaitu, ruang memori fisik 8086 dalam mode virtual 8086.

Grup Kesalahan FPU

FERR Sinyal keluaran FERR diaktifkan setiap kali unit titik mengambang menghasilkan kesalahan apa pun.

IGNNE Ketika pin input IGNNE (Ignore Numeric Processor Extension) diaktifkan, 80486 mengabaikan kesalahan prosesor mengambang (FPU) dan mengeksekusi instruksi floating-point non-kontrol secara terus-menerus.

Grup Port Akses Uji Akses uji adalah fasilitas unik yang tersedia dalam versi 50 MHz 80486. Sinyal akses uji digunakan untuk memeriksa kondisi kesalahan komponen pada motherboard.

TDI Input TDI (data uji) dari 80486 adalah pin input serial yang digunakan untuk menggeser instruksi dan data JTAG ke dalam komponen.

TCK Input TCK (jam uji) menyediakan sinyal jam dasar, yang diperlukan oleh fitur uji batas.

TDO Pin TDO (test data output) adalah pin keluaran serial yang digunakan untuk menggeser instruksi JTAG dan data keluar dari komponen yang diuji.

TMS Input TMS (pemilihan mode pengujian) didekodekan oleh JTAG TAP (port akses ketuk) untuk memilih operasi logika pengujian ini.

Jalur Pasokan

V CC Pin V CC terhubung ke catu daya +5 V. Terdapat 24 pin V CC pada prosesor 80486. Jalur Ground

V SS Pin V SS terhubung ke terminal ground catu daya. Terdapat 28 pin V SS pada prosesor 80486.

Komentar

Posting Komentar